Interview Question 8: Sneaking CPU read/writes when continuous Memory Read Writes are going on

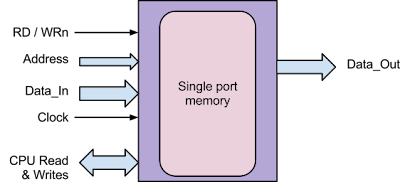

With the advent of increased performance needs new design challenges arise. This questions deals with one of such problem. A single port memory is continuously accessed by surrounding data plane blocks. They are accessing memory in continuous fashion. For example W-R-W-R.... There is no empty clock cycle to waste.

The software wants to access this memory through CPU read/writes intermittently. Usually a simple mechanism using a state machine can be used to sneak in CPU access when no data plane access is going on. The problem arises when when this request gets timed out as every clock is being used by data planes accesses. How does one resolve this problem?

Changing single port memory to dual port memory seems to be easy solution but what if it is prohibitively expensive and not allowed. As design geometries are also stretched to the limit, increasing/doubling clock rate of memory is also ruled out.

How will you approach this practical problem?