Interview Question 7: Enhance the memory

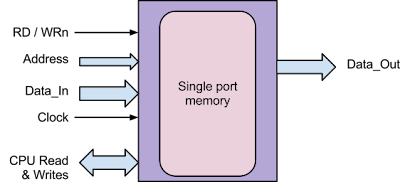

You are given a one port memory block as shown below.

In past you used this memory to design an application where you performed one read or write operation every clock. Now in next generation product you are asked to double the performance. How will you accomplish it? Brainstorm multiple scenarios.

For example:

1. How will you modify the design if you could double the clock at which memory can run?

2. What if you can not double the clock speed? How will you modify the design if you are asked to use memory at the same clock period as the surrounding logic.

I know, it is difficult to take out juice from the memory like this. What if you are asked just to allow (WRx + RDy) or (RD0 + RD1) combinations only? You may also use more than one memory to solve this problem.